|

|

|

|

Intel 90nmプロセス情報

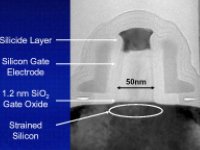

90nm process transistor | Intelは2003年の導入を予定している90nmプロセステクノロジの詳細を発表した。Intelではこの90nmプロセスで"Strained silicon"を採用しトランジスタの動作速度を向上させるほか、配線間の静電容量を抑えるlow-k誘電体としてカーボン膜を使用、0.13μプロセスで使用しているSiOFと比べ静電容量を18%ほど抑えチップの動作速度を向上させるという。

90nmプロセス製品の量産はまずD1Cファブで開始され、2003年中には他の300mmファブも90nmへと移行する。90nmプロセス製造による製品は、2003年下半期よりPrescott、Nocona、およびDothanが投入される予定。 |

- 1.2nmゲート酸化膜 (原子5個程度の厚さ)

- Strained silicon: トランジスタの動作速度を10-20%向上

- 50nmゲート長

- 動作電圧 1.2V以下

- 7層銅配線

- Carbon-doped oxide (CDO)

| |

|